Scan и BIST относятся к двум технологиям в категории DFT. Суть все-таки в дизайне, потому что эти две технологии фактически будут генерировать аппаратные схемы в чипе, но они не являются никакими функциями, и они предназначены специально для тестирования.

Scan Design

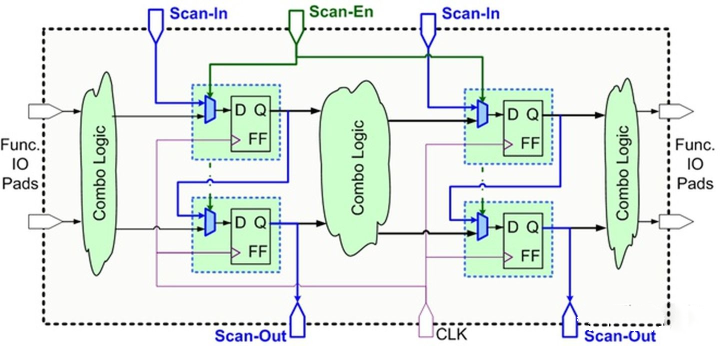

Технология сканирования была впервые предложена Kobayashi et al. Его преимущество заключается в том, что основной принцип заключается в том, что последовательные схемы могут быть смоделированы как сеть комбинационных цепей.

Цель проектирования Scan состоит в том, чтобы улучшить управляемость и наблюдаемость.

Вставив некоторую дополнительную аппаратную схему между логикой A и логикой B, можно наблюдать и контролировать значение, передаваемое из логики A в логику B.

="/uploads/images/202211280015495dc458032.png" alt="202211280015495dc458032.png"/>scan разделен на два этапа:

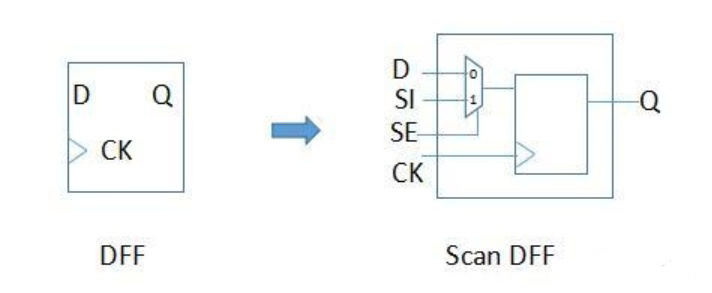

1. Scan replacement: Замените обычный DFF на Scan DFF. На следующем рисунке показан мультиплексор D DFF. Вы можете видеть, что есть дополнительные СИ, SE и мультиплексор.

Когда значение клеммы SE равно 0, схема работает в нормальном функциональном состоянии и может фиксировать значение клеммы D; когда SE равно 1, схема работает в так называемом режиме сканирования и фиксирует значение SI.

<p style="text-align: center;">

Существует три общие ячейки сканирования:

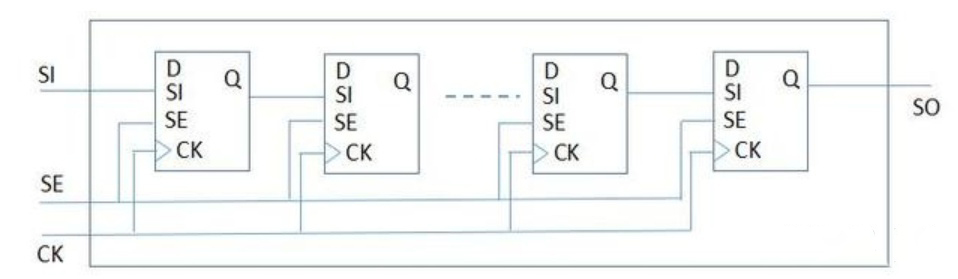

2. Сканирование сшивания: Сканирование сшивания заключается в соединении Q и SI сканирующего DFF, полученного на предыдущем шаге, для формирования цепочки сканирования. На верхнем слое чипа расположены глобальные сигналы SE, а также входные и выходные сигналы цепочки сканирования: SI и SO. Благодаря непрерывному действию цепи сканирования задача может быть преобразована из тестирования сложных последовательных схем в тестирование комбинационных схем.

В реальном дизайне эти два шага выполняются инструментами EDA.

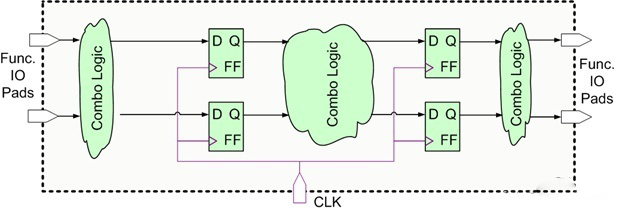

Два приведенных выше рисунка имеют только последовательные единицы, и мы поместим комбинационную логику.

Перед сканированием После вставки скана

После вставки скана

>Шаги теста сканирования

:1. Установите Scan-En на 0, после чего схема будет работать в нормальном состоянии (функциональный режим), и вставка сканирования не повлияет на нормальную работу схемы.

2. Установите Scan-En на 1, затем включите часы для управления регистром, введите тестовые данные на терминале Scan-In, а затем наблюдайте на выходе terminal Scan-Out. Этот метод может протестировать Flip-Flop.

3. При тестировании комбинационной логики установите Scan-En на 1, затем включите часы для управления регистром, введите тестовые данные на терминале Scan-In, и после двух тактов данные будут отправлены на входной терминал комбинационной логики.

4. Затем установите Scan-En в 0, часы бьют, и выходное значение комбинационной логики будет отправлено в регистр справа.

5. Установите для параметра Scan-En значение 1, и цепочка сканирования будет работать в режиме смены. В это время выходное значение комбинаторной логики можно сдвинуть и сравнить с ожидаемым значением.

="/uploads/images/20221128001549f53b30825.png" alt="20221128001549f53b30825.png"/>BIST -- встроенная самопроверка

Встроенная технология самотестирования (BIST) добавляет некоторые дополнительные схемы самотестирования в конструкцию чипа, и нужно только подать необходимые управляющие сигналы извне для проверки тестируемой схемы путем запуска встроенного аппаратного и программного обеспечения самотестирования. дефекты или неисправности. В отличие от конструкции сканирования, встроенная самодиагностика может упростить этапы тестирования и не требует дорогостоящих контрольно-измерительных приборов и оборудования (например, оборудования ATE), но увеличивает сложность конструкции микросхемы.

BIST можно условно разделить на две категории: Logic BIST (LBIST) и Memory BIST (MBIST) LBIST обычно используется для тестирования. Как правило, генератор псевдослучайных тестовых шаблонов используется для генерации входных тестовых шаблонов, которые применяются к внутреннему механизму устройство; и (MISR) используется в качестве генератора выходного сигнала. MBIST используется только для тестирования памяти, типичный MBIST содержит тестовые схемы для загрузки, чтения и сравнения тестовых шаблонов. В настоящее время в отрасли широко используется несколько алгоритмов MBIST, таких как алгоритмы «March», March-C и MATS+. Еще один относительно редкий BIST называется Array BIST, который является разновидностью MBIST и специально используется для самотестирования встроенной памяти. Аналог BIST, используется для самотестирования. Технология BIST становится альтернативой дорогостоящим ATE, но технология BIST не может полностью заменить ATE в настоящее время, и они будут сосуществовать в течение длительного времени в будущем. Scan и BIST - две очень важные технологии в проектировании тестируемости чипов, и они также являются необходимыми навыками для инженера DFT.