В прошлом компромиссы между производительностью, мощностью и стоимостью в основном определялись крупными OEM-производителями в рамках industrY-wide Roadmaps расширения. Производители микросхем разрабатывают чипы в соответствии с узкими спецификациями, выдвинутыми этими OEM-производителями. Но по мере того, как закон Мура замедляется, и по мере того, как все больше датчиков и электроники генерируют больше данных повсюду, цели проектирования и средства их достижения меняются.

Некоторые из крупнейших системных компаний уже разрабатывают чипы собственными силами, чтобы сосредоточиться на конкретных типах данных и вариантах использования. В то же время традиционные производители чипов создают гибкие архитектуры, которые могут Их можно использовать повторно и легко модифицировать для более широкого спектра применений.

В этом новом дизайне скорость, с которой необходимо обрабатывать данные, и точность результатов могут сильно различаться. В зависимости от ситуации — например, будет ли он использоваться в приложениях безопасности или критически важных приложениях, или если он находится рядом с другими компонентами, которые могут выделять тепло или шум, — архитекторы могут взвесить сырую производительность, производительность на ватт и общую стоимость владения, включая надежность и безопасность. Это, в свою очередь, определяет тип инкапсуляции, память, компоновку и требуемую избыточность.

На недавней конференции Hot Chips 34 старший главный инженер NVIDIA Джек Чокетт (Jack Choquette) представил новые 80-миллиардные транзисторные графические процессоры компании. Новая архитектура учитывает пространственную локальность, которая позволяет обрабатывать данные из разных мест доступными элементами обработки, и временную локальностьy, где несколько ядер могут работать с данными.

="/uploads/images/2022101219314570b669890.png" alt="2022101219314570b669890.png" width="884" height="397" style="width: 884px; height: 397px;"/>

Цель состоит в том, чтобы позволить большему количеству блоков работать с фрагментами данных синхронно или асинхронно для большей эффективности и скорости. Это контрастирует с существующими подходами, когда все потоки должны ждать поступления других данных, прежде чем начнется обработка.

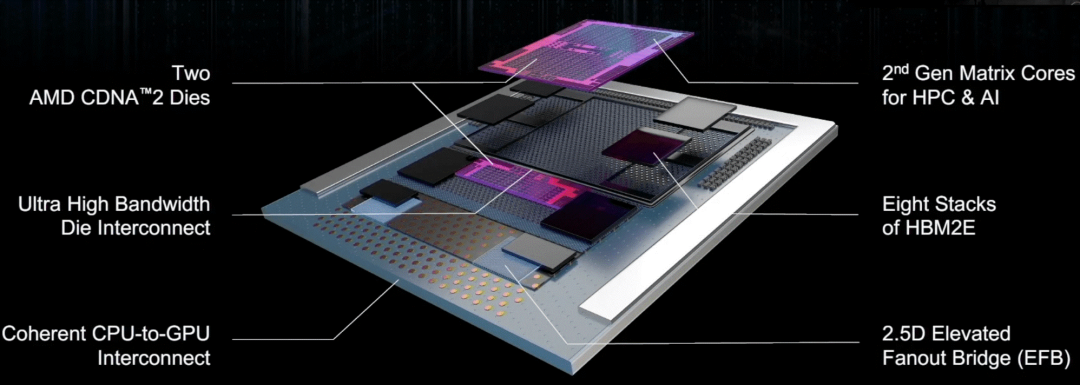

В дизайне AMD путь к данным расширен для пересылки и повторного использования данных. Как и в случае с архитектурой NVIDIA, цель состоит в том, чтобы устранить узкие места в пути передачи данных, упростить операции и улучшить использование различных вычислительных элементов. Для повышения производительности AMD устраняет необходимость постоянного копирования для резервного копирования памяти, значительно сокращая перемещение данных.

Новые чипы AMD Instinctвключают гибкий высокоскоростной ввод-вывод и 2.5D-мост, соединяющий различные вычислительные элементы. Высокоскоростные мосты были впервые коммерциализированы Intel со встроенным мостом EMIB (Embedded Multi-Die Interconnect Bridge), который позволяет двум или более чипам действовать как один. Apple использовала этот подход, соединив две SoC M1 на базе Arm для создания своего чипа M1 Ultra.

Все эти архитектуры более гибкие, чем предыдущие версии, а подход chiplet/tile предлагает крупным производителям микросхем способ настройки чипов, при этом обслуживая широкую клиентскую базу.

Архитектура чипа центра обработки данных Tesla является хорошим примером того, как они хотят иметь возможность использовать преимущества нескольких уровней параллелизма - параллелизма на уровне данных и модели на уровне обучения, как а также присущий параллелизм, который выполняется при обучении сверткам и матричным умножениям Параллелизм в операциях. Мы хотим, чтобы это было полностью программируемое и гибкое оборудование.

The Difference

ASIC всегда были кастомными, но с каждым новым технологическим узлом затраты росли до такой степени, что для окупаемости затрат на проектирование и производство хватает только самого большого объема приложений, таких как смартфоны или ПК.Чтобы выжать более высокую производительность на ватт из этих конструкций, они также оптимизируют чип для конкретных функций программного обеспечения и того, как программное обеспечение использует аппаратное обеспечение - сложный и часто итеративный процесс, который требует постоянной тонкой настройки посредством регулярных обновлений программного обеспечения.

Чтобы сэкономить электроэнергию и затраты, проектные группы расставляют приоритеты для различных функций в зависимости от приложения, а затем упаковывают несколько микросхем вместе или разделяют их в одну SoC в зависимости от конкретных целей проектирования.

По мере того, как все больше производителей микросхем применяют подход чиплетов, им необходимо учитывать сочетание критических и некритических путей данных. Это включает в себя все: от соображений шума до смещения стружки в корпусах, коэффициентов теплового расширения из-за различных материалов в этих корпусах и технологических изменений в самих компонентах. В то время как такие компании, как Arm, Synopsys (процессоры ARC) и растущее число поставщиков RISC-V, проводят тщательную работу над своей интеллектуальной собственностью, количество пограничных случаев и потенциальных взаимодействий увеличивается.

Все это усложняет процесс проектирования, проверки и отладки и может создать проблемы в производстве, если количество и понимание Там, где могут возникнуть аномалии, недостаточно. Это объясняет, почему все больше и больше компаний, занимающихся САПР, интеллектуальной собственностью, тестированием/анализом и безопасностью, предлагают услуги, дополняющие работу внутренних проектных групп.

"Больше нет необходимости проектировать процессор для выполнения функций x, y и z для каждой рабочей нагрузки без учета накладных расходов», - сказал Сайлеш Читтипедди, исполнительный вице-президент Renesas Electronics. «Вот почему все эти компании сейчас более вертикальны. Они предлагают решения, которые им нужны. Это включает в себя искусственный интеллект на системном уровне. Он включает в себя взаимодействие между электрическими и механическими свойствами, вплоть до того, где вы размещаете конкретный разъем. Это также побуждает все больше компаний, занимающихся САПР, переходить на поддержку системного уровня и проектирование на системном уровне».

Этот сдвиг происходит на растущем числе вертикальных рынков, от мобильных телефонов и автомобилей до промышленного оборудованияCations, и это приводит к волне небольших приобретений далеко за пределами радара, поскольку производители чипов стремятся нацелить свое оборудование на широкий спектр новых рынков.

Тем не менее, решения, ориентированные на предметную область, усилили давление на компании, занимающиеся EDA, с целью выявления общих черт, которые можно автоматизировать. Гораздо проще использовать планарные чипы, разработанные на одном технологическом узле. Но по мере того, как все больше и больше рынков становятся цифровыми — будь то автомобильные, промышленные, военные/авиационные, коммерческие или потребительские — их цели становятся все более разными.

Ожидается, что эта разница будет только увеличиваться по мере того, как чиплеты, разработанные на разных узлах процесса, разрабатываются для пользовательских пакетов, которые могут быть основаны на всем, от разветвленных столпов до полных реализаций 3D-IC. В некоторых случаях может быть даже комбинация 2.5D и 3D-IC, которую Siemens EDA обозначил как 5.5D.

Хорошие новости для EDA и IP-компании считают, что это значительно увеличило потребность в симуляции, симуляции, прототипировании и моделировании. Крупные поставщики систем также оказывают давление на поставщиков EDA, чтобы автоматизировать процесс проектирования для большего количества системных компаний, но их недостаточно, чтобы оправдать такие инвестиции. Вместо этого системные компании обратились к компаниям, занимающимся САПР и ИС, для предоставления экспертных услуг, перейдя от транзакционных отношений к более глубоким партнерским отношениям и предоставив компаниям, занимающимся САО, более глубокое понимание того, как и где используются различные инструменты. Уязвимости для новых возможностей.

"Многие новые игроки более вертикально интегрированы, поэтому они больше работают собственными силами», - сказал Нильс Фаше, вице-президент и генеральный менеджер по проектированию и моделированию в Keysight. «Существует гораздо больший интерес к моделированию на системном уровне, и потребность в совместных рабочих процессах внутри компаний и между ними растет. Мы также видим больше дизайнатерации. Таким образом, у вас есть команда разработчиков, команда качества, и вы постоянно обновляете дизайн».

Для компаний, производящих чипы, разрабатывающих чипы для OEM-производителей, это только часть проблемы. "Если вы посмотрите на автомобильный рынок, то увидите, что речь идет уже не о разработке чипсета", - сказал Фаше. «На начальных этапах компания-производитель чипов может использовать программное обеспечение для создания эталонного проекта и настройки его в зависимости от того, как оно используется. Затем OEM-производитель будет стремиться к оптимизации. При этом он подталкивает сотрудничество вверх по традиционной пищевой цепочке. Например, если вы разрабатываете радарный чип, то это не просто радиолокационная подсистема. Это радар в контексте более крупного технологического стека».

Стек может включать в себя радиочастотные пакеты, антенны и приемники, в то время как OEM-производитель создает радиостанцию с использованием EDA.

Application specific and general

Большая проблема для команд дизайнеров заключается в том, что все больше дизайнов становятся интерфейсными. Вместо того, чтобы просто создавать архитектуру чипа, а затем обращаться к деталям в процессе проектирования, необходимо решить больше проблем на архитектурном уровне.

"Было время, когда компания по производству чипов поставляла чипы, которые потребляли слишком много энергии, и OEM-производители были недовольны этим», - сказал Джо Савицкий, исполнительный вице-президент Siemens Digital Industries Software. "Но вы бы не знали, как просто запускать приложения. Искусственный интеллект позволяет Эта проблема становится больше, потому что это не просто проблема программного обеспечения. Теперь вы можете запустить все эти выводы на нем. Если вас не волнует задержка, вы можете поставить универсальную чип в облаке, и вы просто разговариваете с облаком И получаете данные обратно. Но если у вас есть что-то в режиме реального времени, и оно должно немедленно отреагировать, вы не можете позволить себе такую задержку и вам нужно низкое энергопотребление. Так что, по крайней мере, для ускорителей вам нужен индивидуальный дизайн».

Гордон Купер, менеджер по маркетингу продуктов в Synopsys, соглашается. «Если вы используете ИИ, используете ли вы его в 100 процентах случаев или вы счастливы, что он у вас есть? Если я просто хочу сказать, что у меня есть ИИ на моем чипе, возможно, мне просто нужно использовать DSP для ИИ», — сказал он. Сказать. «Есть компромисс, это зависит от контекста. Если вы хотите получить полноценный ИИ в 100% случаев, возможно, вам нужно добавить внешний IP-адрес или дополнительный IP-адрес».

Большой проблемой для ИИ является поддержание устройств в актуальном состоянии, поскольку алгоритмы постоянно обновляются. Это становится сложнее, если дизайн является одноразовым, и все оптимизировано для одного или нескольких алгоритмов. Таким образом, в то время как архитектуры должны быть масштабируемыми С точки зрения производительности, они также должны быть масштабируемыми с течением времени и в контексте других компонентов системы.

Обновления программного обеспечения могут нанести ущерб часам. «Все, что вы делаете с качеством синхронизации чипа, влияет на задержку, производительность, энергопотребление и время выхода на рынок», — сказал генеральный директор Movellus Мо Фейсал в презентации на саммите AI Hardware Summit 2022 года. - Чипы размером с сетку - вы можете оптимизировать ядро и убедиться, что оно хорошо работает с программным обеспечением. Это умножение матрицы, вычисление графов, чем больше ядер вы бросите в него параллельно, тем лучше. Однако сейчас эти чипы сталкиваются с проблемами. Раньше это было проблемой для одной-двух команд в Intel и AMD, теперь это проблема всех. "

Синхронизация всего становится процессом, а не отдельной функцией. " У вас могут быть разные рабочие нагрузки,— сказал Фейсал. Таким образом, вы можете просто захотеть использовать 50 ядер для одной рабочей нагрузки, а для следующей рабочей нагрузки вы захотите использовать 500 ядер. Но когда вы включаете следующие 500 ядер, вы в конечном итоге нагружаете сетку и приводите к спаду».

Также есть проблема с шумом переключения. В прошлом некоторые из этих проблем можно было решить с помощью резервирования. Но в продвинутых узлах этот запас увеличивает время и энергию, необходимые для перемещения электронов по очень тонким проводам, что, в свою очередь, создает сопротивление и увеличивает рассеивание тепла. Таким образом, компромиссы для каждого нового узла становятся более сложными, а взаимодействия между различными компонентами в пакете являются аддитивными.

"Если вы посмотрите на 5G, это означает нечто иное для автомобиля, чем для центра обработки данных или потребителя», - сказал в интервью Фрэнк Ширрмайстер, директор по маркетингу продуктов в Cadence. «Все они имеют разную пропускную способность. Вame идет на AI/ML. Это зависит от домена. Затем, поскольку все гиперсвязано, это не только в одном домене. Таким образом, это, по сути, требует много вариантов одного и того же чипа , вот где гетерогенная интеграция становится интересной. Общая дезинтеграция SoC пригодится, потому что вы можете выполнять разные уровни производительности в зависимости от таких вещей, как биннинг. Но это уже не дизайн сам по себе, потому что некоторые правила больше не применяются».

In Conclusion

Вся экосистема проектирования чипов постоянно меняется, и это распространяется вплоть до программного обеспечения. В прошлом проектные группы могли гарантировать, что программное обеспечение, написанное на высоком уровне абстракции, будет работать хорошо, с регулярными улучшениями при введении каждого нового узла.

Производители чипов разрабатывают планы, чтобы сделать их очень специфическими или достаточно универсальными, чтобы иметь возможность использовать свои архитектуры в нескольких проектах.