Overview Устройство SN74LVC1G17 содержит один триггерный буфер Шмитта и выполняет логическую функцию Y = A. Устройство функционирует как an independent buffer, но из-за действия Шмитта оно будет иметь другие пороговые уровни ввода для a positive-going (VT+) и отрицательные сигналы. Технология упаковки DPW является крупным прорывом в упаковке микросхем. Его крошечная площадь 0,64 мм экономит значительное пространство на плате по сравнению с другими вариантами корпуса, сохраняя при этом традиционный удобный для производства шаг свинца 0,5 мм. Это устройство полностью предназначено для приложений с частичным отключением питания с использованием Ioff. Схема Ioff отключает выходы, предотвращая повреждение обратного потока тока через устройство при выключенном питании.

Feature Description • Широкий диапазон рабочего напряжения.

– работает от 1,65 В до 5,5 В.

• Позволяет преобразовывать пониженное напряжение.

<span style=";font-family:宋体;font-size:16px">• Входы принимают напряжения в 5.5 V.

• Функция Ioff допускает напряжения на входах и выходах, когда VCC равен 0 В.

<p style="margin-top: 7px;margin-bottom: 7px">

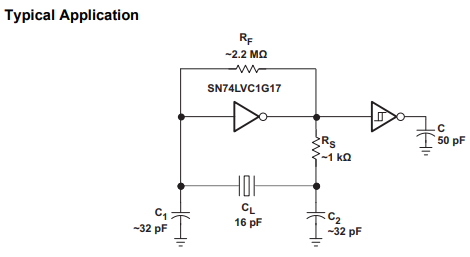

>Application Информация

SN74LVC1G14 - это КМОП-устройство с высоким диском, которое можно использовать для множества функций буферного типа, когда вход медленный или шумный. Он может производить 24 мА тока привода при 3.3 V что делает его идеальным для управления несколькими выходами и подходит для высокоскоростных приложений до 100 MHz. Входы устойчивы к напряжению 5,5 В, что позволяет переводить его в VCC.

<p style="margin-top: 7px;margin-bottom: 7px">

Layout Guidelinesstrong>

1. При использовании нескольких устройств битовой логики входные данные никогда не должны плавать.

style="margin-top: 7px;margin-bottom: 7px">2. Во многих случаях функции или части функций цифровых логических устройств не используются, например, когда используются только два входа вентиля с тройным входом И или только 3 из 4 буферных вентилей.

style="margin-top: 7px;margin-bottom: 7px">3. Такие входные клеммы не следует оставлять неподключенными, поскольку неопределенные напряжения на внешних соединениях приводят к неопределенным рабочим состояниям.

4. Ниже приведены правила, которые должны be observation при любых обстоятельствах. 5. Все неиспользуемые входы цифровых логических устройств должны быть подключены к высокому или низкому смещению, чтобы предотвратить их плавающее смещение. style="margin-top: 7px;margin-bottom: 7px">6. Логический уровень, который должен быть применен к любому конкретному неиспользуемому входному приложениюDS о функциях устройства. style="margin-top: 7px;margin-bottom: 7px">7. Как правило, они будут привязаны к Gnd или VCC, в зависимости от того, что имеет больше смысла или удобнее.

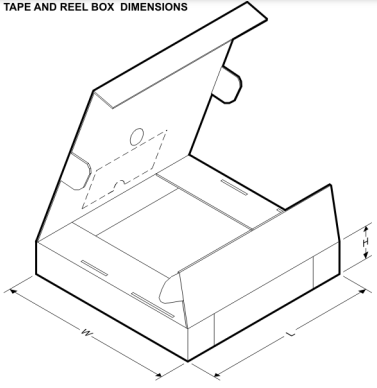

Механическая, упаковочная и упорядоченная информация Следующие страницы включают в себя: механическая упаковка and orderable information. Эта информация является самыми последними данными, доступными для назначенных устройств. Эти данные могут быть изменены без предварительного уведомления и пересмотра этого документа. Для браузерных версий этого технического описания см. Панель навигации слева.